Production documentation of printed circuits consists of:

- Gerber files of the PCB project with drilling files,

- laminate specification taking into account the stack-up,

- information on additional requirements such as Tg (glass transition temperature), base material or impedance check.

While designing a stack-up of a multi-layer printed circuit, additional factors due to the technological limitations of the production process should be taken into account. One should also strive for the stack-up to be symmetrical, because it will avoid problems with uncontrolled bending of the laminate after the production or assembly process.

The final thickness of the laminate

In the case of lamellas with a HAL pad surface coating (HASL), the minimum PCB thickness cannot be less than 0.8 mm – due to the high temperature of the process, the risk of bending of the laminate increases.

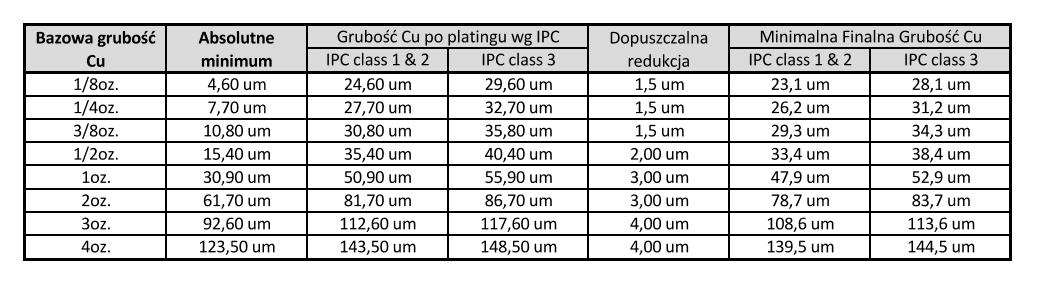

Core and Prepreg dielectric layers

The suggested number of core layers (laminate core) in the multilayer circuit is calculated according to the formula L / 2 – 1, where L is the number of Cu layers. And so for a 4-layer stack-up laminate, one of the core layers (between layers L2 and L3) and 2 prepreg layers (between L1 and L2 and L3 and L4) is constructed. For 8-layer PCBs, 3 core layers are used, 12 layers of 5 core layers.

Typical stack-up designs for multilayer printed circuits::

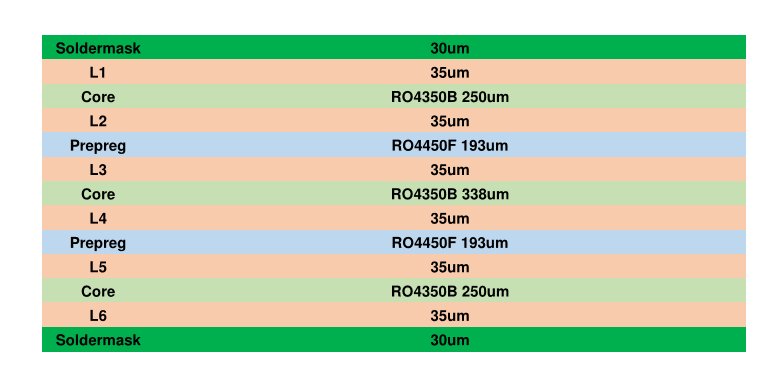

Typical layered layers have limited application in the case of PCB production on special materials, such as ROGERS or ISOLA. The production specifications on such materials contain additional requirements, such as line impedance control and differential pairs. In such cases, the dielectric thicknesses are selected to meet the impedance requirements. We always confirm the final stack-up project with our clients.

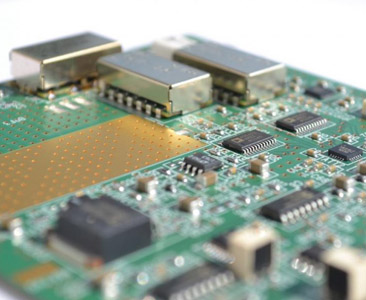

An example of the implementation of a printed circuit on ROGERS RO4350B material with impedance control of differential pairs on external layers.

Stack-up 6-layer PCB, ROGERS RO4350B

The final thickness of the laminate 1.5mm, thickness Cu 35um

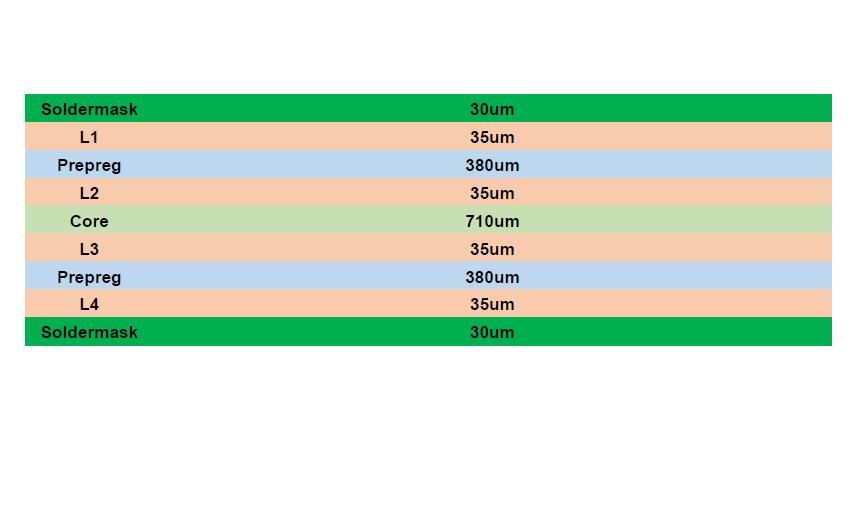

In the case of production of prototype 4-layer printed circuits with an express deadline, we use a stack-up based on NanYa NP140 material. The final thickness of the printed circuit at a Cu 35um thickness is 1.55mm.